Boot using U-Boot

QNX Board Support Packages8.0BSP User's GuideTI Jacinto 7 J784S4 Evaluation ModuleTexas InstrumentsTexas InstrumentsARM

You must first boot the board with U-Boot from the microSD card. After U-Boot launches, you can load the QNX IFS.

- For information about how to boot U-Boot and then load the QNX IFS using an microSD card, see the

Load the QNX IFS from the microSD card section in this chapter.

Load the QNX IFS from the microSD card

The followings steps describe how to boot board using U-Boot and then load the QNX IFS from your microSD card. Before you can complete these steps, you must prepare the microSD card. For more information, see thePreparing the microSD card to boot the boardsection in this chapter for more information.

- Connect your Jacinto 7 J784S4 EVM target board to your host system.

- On your host machine, start your favorite terminal program with these settings:

- Serial Device: /dev/ttyUSB0

- Baud rate: 115200

- Data: 8 bit

- Parity: none

- Stop: 1 bit

- Flow control: none

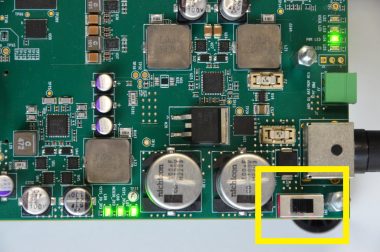

- Connect the Jacinto 7 J784S4 EVM board to the power supply. The power is controlled with the ON/OFF switch beside the power connector. To turn the board ON, slide the switch in the direction towards the center of the board. You should see lights appear below the ON/OFF switch.

Figure 1Power ON/OFF switch

- After the power is turned on, output from U-Boot appears on the terminal console. When you see the prompt

Hit any key to stop autoboot

, press any key on your keyboard to interrupt the boot process as follows:U-Boot SPL 2025.01-00410-g70667128cb5b (Apr 04 2025 - 18:20:14 +0000) SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') Initialized 4 DRAM controllers SPL initial stack usage: 13456 bytes Trying to boot from MMC2 Skipping authentication on GP device Skipping authentication on GP device Skipping authentication on GP device Skipping authentication on GP device Skipping authentication on GP device Loading Environment from nowhere... OK Starting ATF on ARM64 core... NOTICE: BL31: v2.12.0(release):11.00.09-dirty NOTICE: BL31: Built : 12:35:58, Mar 24 2025 I/TC: I/TC: OP-TEE version: 4.5.0-73-gef1ebdc23-dev (gcc version 13.3.0 (GCC)) #1 Tue Feb 4 11:33:18 UTC 2025 aarch64 I/TC: WARNING: This OP-TEE configuration might be insecure! I/TC: WARNING: Please check https://optee.readthedocs.io/en/latest/architecture/porting_guidelines.html I/TC: Primary CPU initializing I/TC: GIC redistributor base address not provided I/TC: Assuming default GIC group status and modifier I/TC: SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') I/TC: Activated SA2UL device I/TC: Fixing SA2UL firewall owner for GP device I/TC: Enabled firewalls for SA2UL TRNG device I/TC: SA2UL TRNG initialized I/TC: SA2UL Drivers initialized I/TC: HUK Initialized I/TC: Primary CPU switching to normal world boot U-Boot SPL 2025.01-00410-g70667128cb5b (Apr 04 2025 - 18:20:14 +0000) SYSFW ABI: 4.0 (firmware rev 0x000b '11.0.9--v11.00.09+ (Fancy Rat)') Trying to boot from MMC2 Skipping authentication on GP device Skipping authentication on GP device U-Boot 2025.01-00410-g70667128cb5b (Apr 04 2025 - 18:20:14 +0000) SoC: J784S4 SR1.0 GP Model: Texas Instruments J784S4 EVM DRAM: 2 GiB (total 32 GiB) mmio-mux mux-controller@4080: unable to set idle state Core: 143 devices, 35 uclasses, devicetree: separate Flash: 0 Bytes MMC: mmc@4f80000: 0, mmc@4fb0000: 1 Loading Environment from nowhere... OK In: serial@2880000 Out: serial@2880000 Err: serial@2880000 am65_cpsw_nuss ethernet@46000000: K3 CPSW: nuss_ver: 0x6BA02102 cpsw_ver: 0x6BA82102 ale_ver: 0x00293904 Ports:1 Net: eth0: ethernet@46000000port@1 => - On the U-Boot prompt, type the following U-Boot commands to load the QNX IFS from the microSD card:

- mmcinfo

- fatload mmc 1 88000000 psdk_linux_9.2_k3-j784s4-evm.dtb

For Quad Ethernet expansion board support, use:

fatload mmc 1 88000000 psdk_linux_9.2_k3-j784s4-evm-quad-port-eth-exp1.dtb - fatload mmc 1 80080000 qnx-ifs

- go 80080000 88000000

=> mmcinfo Device: mmc@4f80000 Manufacturer ID: 13 OEM: 4e Name: S0J56X Bus Speed: 200000000 Mode: HS400 (200MHz) Rd Block Len: 512 MMC version 5.1 High Capacity: Yes Capacity: 14.8 GiB Bus Width: 8-bit DDR Erase Group Size: 512 KiB HC WP Group Size: 8 MiB User Capacity: 14.8 GiB WRREL Boot Capacity: 31.5 MiB ENH RPMB Capacity: 4 MiB ENH Boot area 0 is not write protected Boot area 1 is not write protected => fatload mmc 1 88000000 psdk_linux_9.2_k3-j784s4-evm.dtb 87718 bytes read in 29 ms (2.9 MiB/s) => fatload mmc 1 80080000 qnx-ifs 12992012 bytes read in 569 ms (21.8 MiB/s) => go 80080000 88000000 ## Starting application at 0x80080000 ... Hypervisor support disabled MMU: 16-bit ASID 44-bit PA TCR_EL1=00000014b5183519 ARM GIC-500 r1p1, arch v3.0 detected gic_v3_lpi_add_entry for vectors 8192 -> 8447, Ok gic_v3_lpi_add_entry for vectors 8448 -> 65535, Ok No SPI intrinfo. Add default entry for 32 -> 991 vectors, Ok LPI config table #1 @ 0000000080013000, callout vaddr: ffffff8040311000 aarch64_cpuspeed: core speed 2000 cpu0: MPIDR=0000000080000000 cpu0: MIDR=411fd080 Cortex-A72 r1p0 cpu0: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT cpu0: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1 cpu0: L1 Icache 48K linesz=64 set/way=256/3 cpu0: L1 Dcache 32K linesz=64 set/way=256/2 cpu0: L2 Unified 2048K linesz=64 set/way=2048/16 Enabling ITS 0 ITS queue at 0000000080030000, num slots: 256 Issue MAPC/SYNC/INVALL commands for ICID 0 update CWRITER to 0x00000060 Waiting for all commands to be processed ... Done in 1 tries Enable LPIs in GICR_CTLR @ 0000000001900000 for CPU0 serdes_init(), 2 entries serdes_lane_cfg_set(0, 0x02020101) SERDES0 Lane Config ... Ok serdes_lane_cfg_set(0, 0x02020101), Ok serdes_enable(0) serdes_enable(0), Ok serdes_misc_init(0, 0000000005060000) serdes_misc_init(0, 0000000005060000), Ok serdes_lane_cfg_set(1, 0x01010101) SERDES1 Lane Config ... Ok serdes_lane_cfg_set(1, 0x01010101), Ok serdes_enable(1) serdes_enable(1), Ok serdes_misc_init(1, 0000000005070000) serdes_misc_init(1, 0000000005070000), Ok serdes_init() Ok init_dp: -=* DSS DPI0 pixel clock frequency is 148500000 HZ *=- Total Available L3 cache (MSMC SRAM): 1048576 bytes Loading IFS...decompressing...done I/TC: Secondary CPU 1 initializing I/TC: Secondary CPU 1 switching to normal world boot aarch64_cpuspeed: core speed 2000 cpu1: MPIDR=0000000080000001 cpu1: MIDR=411fd080 Cortex-A72 r1p0 cpu1: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT cpu1: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1 cpu1: L1 Icache 48K linesz=64 set/way=256/3 cpu1: L1 Dcache 32K linesz=64 set/way=256/2 cpu1: L2 Unified 2048K linesz=64 set/way=2048/16 ITS 0 already Enabled ITS queue at 0000000080030000, num slots: 256 Issue MAPC/SYNC/INVALL commands for ICID 1 update CWRITER to 0x000000c0 Waiting for all commands to be processed ... Done in 1 tries Enable LPIs in GICR_CTLR @ 0000000001920000 for CPU1 I/TC: Secondary CPU 2 initializing I/TC: Secondary CPU 2 switching to normal world boot aarch64_cpuspeed: core speed 2000 cpu2: MPIDR=0000000080000002 cpu2: MIDR=411fd080 Cortex-A72 r1p0 cpu2: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT cpu2: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1 cpu2: L1 Icache 48K linesz=64 set/way=256/3 cpu2: L1 Dcache 32K linesz=64 set/way=256/2 cpu2: L2 Unified 2048K linesz=64 set/way=2048/16 ITS 0 already Enabled ITS queue at 0000000080030000, num slots: 256 Issue MAPC/SYNC/INVALL commands for ICID 2 update CWRITER to 0x00000120 Waiting for all commands to be processed ... Done in 1 tries Enable LPIs in GICR_CTLR @ 0000000001940000 for CPU2 I/TC: Secondary CPU 3 initializing I/TC: Secondary CPU 3 switching to normal world boot aarch64_cpuspeed: core speed 2000 cpu3: MPIDR=0000000080000003 cpu3: MIDR=411fd080 Cortex-A72 r1p0 cpu3: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT cpu3: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1 cpu3: L1 Icache 48K linesz=64 set/way=256/3 cpu3: L1 Dcache 32K linesz=64 set/way=256/2 cpu3: L2 Unified 2048K linesz=64 set/way=2048/16 ITS 0 already Enabled ITS queue at 0000000080030000, num slots: 256 Issue MAPC/SYNC/INVALL commands for ICID 3 update CWRITER to 0x00000180 Waiting for all commands to be processed ... Done in 1 tries Enable LPIs in GICR_CTLR @ 0000000001960000 for CPU3 I/TC: Secondary CPU 4 initializing I/TC: Secondary CPU 4 switching to normal world boot aarch64_cpuspeed: core speed 2000 cpu4: MPIDR=0000000080000100 cpu4: MIDR=411fd080 Cortex-A72 r1p0 cpu4: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT cpu4: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1 cpu4: L1 Icache 48K linesz=64 set/way=256/3 cpu4: L1 Dcache 32K linesz=64 set/way=256/2 cpu4: L2 Unified 2048K linesz=64 set/way=2048/16 ITS 0 already Enabled ITS queue at 0000000080030000, num slots: 256 Issue MAPC/SYNC/INVALL commands for ICID 4 update CWRITER to 0x000001e0 Waiting for all commands to be processed ... Done in 1 tries Enable LPIs in GICR_CTLR @ 0000000001980000 for CPU4 I/TC: Secondary CPU 5 initializing I/TC: Secondary CPU 5 switching to normal world boot aarch64_cpuspeed: core speed 2000 cpu5: MPIDR=0000000080000101 cpu5: MIDR=411fd080 Cortex-A72 r1p0 cpu5: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT cpu5: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1 cpu5: L1 Icache 48K linesz=64 set/way=256/3 cpu5: L1 Dcache 32K linesz=64 set/way=256/2 cpu5: L2 Unified 2048K linesz=64 set/way=2048/16 ITS 0 already Enabled ITS queue at 0000000080030000, num slots: 256 Issue MAPC/SYNC/INVALL commands for ICID 5 update CWRITER to 0x00000240 Waiting for all commands to be processed ... Done in 1 tries Enable LPIs in GICR_CTLR @ 00000000019a0000 for CPU5 I/TC: Secondary CPU 6 initializing I/TC: Secondary CPU 6 switching to normal world boot aarch64_cpuspeed: core speed 2000 cpu6: MPIDR=0000000080000102 cpu6: MIDR=411fd080 Cortex-A72 r1p0 cpu6: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT cpu6: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1 cpu6: L1 Icache 48K linesz=64 set/way=256/3 cpu6: L1 Dcache 32K linesz=64 set/way=256/2 cpu6: L2 Unified 2048K linesz=64 set/way=2048/16 ITS 0 already Enabled ITS queue at 0000000080030000, num slots: 256 Issue MAPC/SYNC/INVALL commands for ICID 6 update CWRITER to 0x000002a0 Waiting for all commands to be processed ... Done in 1 tries Enable LPIs in GICR_CTLR @ 00000000019c0000 for CPU6 I/TC: Secondary CPU 7 initializing I/TC: Secondary CPU 7 switching to normal world boot aarch64_cpuspeed: core speed 2000 cpu7: MPIDR=0000000080000103 cpu7: MIDR=411fd080 Cortex-A72 r1p0 cpu7: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT cpu7: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1 cpu7: L1 Icache 48K linesz=64 set/way=256/3 cpu7: L1 Dcache 32K linesz=64 set/way=256/2 cpu7: L2 Unified 2048K linesz=64 set/way=2048/16 ITS 0 already Enabled ITS queue at 0000000080030000, num slots: 256 Issue MAPC/SYNC/INVALL commands for ICID 7 update CWRITER to 0x00000300 Waiting for all commands to be processed ... Done in 1 tries Enable LPIs in GICR_CTLR @ 00000000019e0000 for CPU7 System page at phys:0000000080022000 user:ffffff8040336000 kern:ffffff8040332000 Starting next program at vffffff806008b4b0 syspage::hypinfo::flags=0x00000000 Welcome to QNX 8.0.0 on TI_J784S4_EVM_Board ! Initializing sciclient in polling mode Starting I2C driver ... Setting OS clock from RTC ... Starting PCI Server ... start serial driver Starting MMC/SD memory card driver... eMMC Starting MMC/SD memory card driver... SD Starting Flash driver... Starting XHCI driver Path=0 - am65x target=0 lun=0 Direct-Access(0) - SDMMC: S0J56X Rev: 1.0 Starting devf-ram filesystem ... Starting networking ... Starting DHCP client ... Starting SSH daemon ... Starting devc-pty manager ... Starting qconn daemon ... Starting shell ... #

You should now be able to test the OS by executing any shell command, or any command residing within the QNX IFS image. For example: ls or uname -a.

Note:

Addresses are interpreted as hexadecimal, therefore entering 0x80080000 and 80080000 are considered to be the same.

Note:

After you've completed the steps above, you can put the following command in the uenv.txt file and then copy it to the board, which permits your system to automatically boot the QNX IFS.

'uenvcmd=mmcinfo; fatload mmc 1 88000000 psdk_linux_9.2_k3-j784s4-evm.dtb; fatload mmc 1 80080000 qnx-ifs; go 80080000 88000000'Page updated: