So where does the clock interrupt come from?

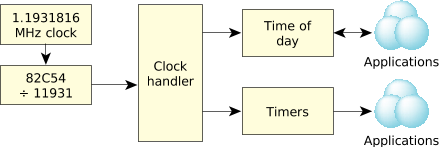

Here's a diagram that shows the hardware components (and some typical values for a PC) responsible for generating these clock interrupts:

Figure 1. PC clock interrupt sources.

Figure 1. PC clock interrupt sources.As you can see, there's a high-speed (MHz range) clock produced by the circuitry in the PC. This high-speed clock is then divided by a hardware counter (the 82C54 component in the diagram), which reduces the clock rate to the kHz or hundreds of Hz range (i.e., something that an ISR can actually handle). The clock ISR is a component of the kernel and interfaces directly with the data structures and code of the kernel itself. On non-x86 architectures, a similar sequence of events occurs; some chips have clocks built into the processor.

Note that the high-speed clock is being divided by an integer divisor. This means the rate isn't going to be exactly 10 ms, because the high-speed clock's rate isn't a multiple of 10 ms. Therefore, the kernel's ISR in our example above might actually be interrupted after 9.9999296004 ms.

Big deal, right? Well, sure, it's fine for our 15-second counter. 15 seconds is 1500 timer ticks—doing the math shows that it's approximately 106 µs off the mark:

15 s - 1500 × 9.9999296004 ms = 15000 ms - 14999.8944006 ms = 0.1055994 ms = 105.5994 µs

Unfortunately, continuing with the math, that amounts to 608 ms per day, or about 18.5 seconds per month, or almost 3.7 minutes per year!

You can imagine that with other divisors, the error could be greater or smaller, depending on the rounding error introduced. Luckily, the kernel knows about this and corrects for it.

The point of this story is that regardless of the nice round value shown, the real value is selected to be the next faster value.